In this blog, we embark on an insightful journey into designing a 4-bit comparator, an essential tool for comparing binary numbers in digital circuits. This practical exploration is part of the curriculum for the CMOS VLSI Design Laboratory, tailored for B.Tech. III Year II Semester students under JNTUH. Utilizing Xilinx Vivado, we will guide you through the entire process of simulating this device. By following a detailed step-by-step approach that combines Verilog coding and FPGA board simulations, this blog aims to provide students with the necessary skills to implement and understand 4-bit comparators, reinforcing key principles of VLSI design and digital logic operations.

Lab Report

AIM: Design of 4 bit Comparator

Apparatus / Software required:

- Xilinx Vivado Design Suite

- Windows Machine

- Notepad or any text editor

Theory:

A 4-bit comparator is a digital circuit that compares two 4-bit numbers, A and B, to see if one is greater than, less than, or equal to the other. It outputs three signals based on this comparison: Greater Than (GT), Less Than (LT), and Equal (EQ). Each number has four bits, A3A2A1A0 and B3B2B1B0.

The comparison starts from the most significant bit (MSB) and moves to the least significant. If the highest bits differ, the comparison of lower bits doesn’t influence the outcome for GT or LT. This step-by-step checking of bits from highest to lowest ensures accurate comparison results.

The table below shows how the comparator’s outputs change based on different combinations of A and B:

| A (Decimal) | B (Decimal) | A3A2A1A0 | B3B2B1B0 | GT | LT | EQ |

|---|---|---|---|---|---|---|

| 8 | 7 | 1000 | 0111 | 1 | 0 | 0 |

| 3 | 3 | 0011 | 0011 | 0 | 0 | 1 |

| 2 | 4 | 0010 | 0100 | 0 | 1 | 0 |

| 15 | 8 | 1111 | 1000 | 1 | 0 | 0 |

| 0 | 9 | 0000 | 1001 | 0 | 1 | 0 |

This simple explanation and the accompanying table are used in the lab manual to guide the practical setup and understanding of how a 4-bit comparator works in a simulated environment like Xilinx Vivado.

Procedure:

- Open Notepad or any text editor on a Windows machine and write the Verilog code for the 8-to-1 multiplexer and 1-to-8 demultiplexer.

- Save the files with a

.vextension, selecting “All Files” as the save type. - Launch Xilinx Vivado from the desktop or start menu.

- Create a new project, naming it appropriately (e.g.,

conparator_4bit) and choosing the project’s storage location. - Ensure “RTL Project” is selected and specify sources at this time by pointing to the Verilog source code and testbench files you’ve created.

- Select the FPGA board or part targeted for this project using the search function.

- Run Behavioral Simulation to compile the Verilog files and execute the simulation based on your testbench.

- Inspect the waveform viewer to verify that the outputs match the expected results based on your testbench scenarios.

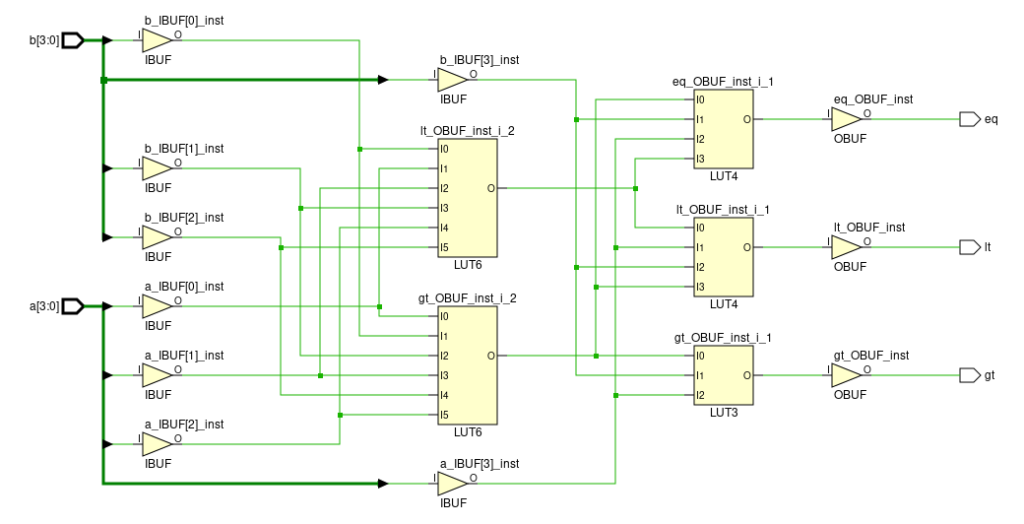

- Proceed with Synthesis and Implementation phases to optimize the design for performance and resource utilization.

- Analyze the simulation results, synthesized schematic, and implementation reports, making necessary adjustments to refine your design.

Results:

After following the steps correctly, the simulation in Xilinx Vivado will show the expected behavior for 4-Bit Comparator, aligning with the input and output relations defined in the theory section.

Code

4-Bit Comparator Verilog Code:

Testbench:

Conclusion:

This lab experiment solidifies the understanding and application of comparators in digital design, showcasing the practical use of Xilinx Vivado in simulating complex VLSI components.

Viva-Voce Questions:

Q1: What is the primary function of a 4-bit comparator?

- The primary function of a 4-bit comparator is to compare two 4-bit binary numbers and determine if one number is greater than, less than, or equal to the other.

Q2: What outputs do you expect from a 4-bit comparator?

- A 4-bit comparator typically outputs three signals: greater than (GT), less than (LT), and equal to (EQ).

Q3: In the context of Vivado, what is the first step in simulating a 4-bit comparator?

- The first step in simulating a 4-bit comparator in Vivado is creating the design file using either VHDL or Verilog code.

Q4: How does a 4-bit comparator determine the greater than condition?

- The comparator checks each bit starting from the most significant bit (MSB) to the least significant bit (LSB). If a higher bit in A is 1 while the corresponding bit in B is 0, A is greater.

Q5: Can you explain what a testbench is and why it is important in simulating a 4-bit comparator in Vivado?

- A testbench is a piece of code used to apply test vectors to the design under test and verify its correctness. It is crucial for simulating a 4-bit comparator to ensure it behaves as expected under different conditions.

Q6: What is the role of synthesis in the design process of a 4-bit comparator in Vivado?

- Synthesis translates the high-level description of the comparator (from VHDL/Verilog code) into a netlist, mapping the logic to specific hardware components available in the FPGA.

Q7: What logic gates can be used to implement a 4-bit comparator?

- Basic logic gates like AND, OR, NOT, and XOR can be used to implement the comparison logic in a 4-bit comparator.

Q8: Why is it important to check the propagation delay in a 4-bit comparator?

- Checking the propagation delay is important to ensure that the output signals (GT, LT, EQ) are generated in a timely manner without causing hold time violations in subsequent circuits.

Q9: What is the significance of the Equal (EQ) output in digital systems using comparators?

- The EQ output is crucial for decision-making processes in digital systems, indicating when two values are identical, which can be essential for error checking and control systems.

Q10: How do you verify the functionality of a 4-bit comparator designed in Vivado?

- The functionality is verified by running simulations in Vivado with different input combinations and checking if the outputs (GT, LT, EQ) match the expected values based on the input conditions.

Complete Detailed Procedure for Simulation in Xilinx Vivado

- Preparation: Before opening Vivado, ensure all Verilog source files and testbenches are correctly written and saved.

- Project Creation: Launch Vivado, create a new project, and specify your project’s name and location.

- Adding Files: Include your Verilog source and testbench files in the project setup.

- Selecting Target Device: Choose the FPGA board or part you’re targeting, based on your project requirements.

- Running Simulation: Utilize the Behavioral Simulation feature to compile and simulate your Verilog files.

- Synthesis and Implementation: After verifying the simulation results, proceed with synthesis and implementation to optimize your design.

- Analysis: Review synthesized schematics, implementation reports, and simulation results to ensure the design meets all criteria.

- Adjustments and Finalization: Make any necessary design adjustments based on your analyses and save your project.

Additional Reading:

- FPGA Design Fundamentals

- Verilog for Beginners

- Advanced Digital Design with the Verilog HDL

FAQ

FAQ: Xilinx Vivado

Here are 10 additional frequently asked questions (FAQs) about Xilinx Vivado that expand beyond the basics previously provided:

- What file formats can Vivado import for FPGA design projects?

- Vivado supports a variety of file formats for import including .v (Verilog), .vhdl (VHDL), .edif (Electronic Design Interchange Format), and .dcp (Design Checkpoint).

- Can Vivado be used for real-time debugging of FPGA circuits?

- Yes, Vivado offers features like the Integrated Logic Analyzer (ILA) and Virtual Input/Output (VIO) for real-time debugging and monitoring of FPGA circuits directly from the software environment.

- What are some of the optimization techniques available in Vivado for FPGA designs?

- Vivado provides several optimization techniques including logic optimization, register balancing, pipelining, and loop unrolling, all aimed at improving the performance and efficiency of FPGA designs.

- How does Vivado handle power analysis and optimization?

- Vivado includes tools for both static and dynamic power analysis as well as power optimization techniques that help designers minimize power consumption in their FPGA designs.

- Does Vivado support partial reconfiguration of FPGAs?

- Yes, Vivado supports partial reconfiguration, allowing users to modify blocks of an FPGA design while the rest of the FPGA continues to operate without interruption.

- What are the simulation capabilities of Vivado?

- Vivado offers both behavioral simulation and post-synthesis timing simulation to validate the functionality and timing of FPGA designs before hardware implementation.

- How does Vivado facilitate design reuse?

- Vivado has robust IP integrator features and a comprehensive IP catalog, which facilitate design reuse by allowing designers to easily integrate and configure pre-built IP blocks into their projects.

- Can Vivado integrate with other software tools for system design?

- Yes, Vivado can integrate with other software tools like MATLAB and Simulink for system-level design, enabling a smoother workflow for complex projects that involve simulation and modeling.

- What are the FPGA design security features available in Vivado?

- Vivado includes features for design security, such as bitstream encryption and secure boot, to protect FPGA designs from unauthorized access and copying.

- How does Vivado support multi-core processing for FPGA design?

- Vivado leverages multi-core processing capabilities of modern CPUs to accelerate various design processes such as synthesis and place-and-route, significantly speeding up design compilation times.

Reference:

- Official Xilinx Vivado Documentation

- Digital Design and Computer Architecture by Harris & Harris

- FPGA Prototyping by Verilog Examples by Pong P. Chu

Here are the reference links formatted for inclusion in your blog:

Internal Links:

- JNTUH VLSI Lab Experiments – Explore a series of lab experiments for understanding VLSI design concepts using Xilinx Vivado.

CMOS VLSI LAB CYCLE 01:

Lab Reports and Related YouTube Videos:

- Lab 01: Logic Gates

- Lab 02: Encoder and Decoder

- Lab 03: Multiplexer, Demultiplexer

- Lab 04: Binary to Gray Converter

CMOS VLSI LAB CYCLE 02:

Lab Reports and Related YouTube Video:

- Lab 01 Part-2: Basic Logic Gates Layout

These resources provide a comprehensive overview and practical insights into various aspects of CMOS VLSI design, offering valuable information for students and enthusiasts interested in exploring the field of VLSI design using Xilinx Vivado and Microwind.